SmartFusion2 MSS

SmartFusion2 MSS

Membuat Desain Menggunakan Antarmuka Fabric MSS

Panduan Pengguna

Perkenalan

Sub-Sistem Mikrokontroler (MSS) SmartFusion2 menawarkan empat Pengontrol Antarmuka Fabric (FIC) yang berbeda:

- DDR_FIC

- SMC_FIC

- FIC_0 dan FIC_1, bergantung pada perangkat Anda

Blok antarmuka ini memungkinkan MSS untuk berinteraksi dengan logika yang diimplementasikan dalam struktur FPGA dan sebaliknya

sebaliknya.

DDR_FIC digunakan ketika Anda mengkonfigurasi blok MSS DDR (MDDR) seperti DDR eksternal

memori dapat diakses dari master fabric FPGA melalui antarmuka AXI atau 2 antarmuka AHBLite AMBA.

SMC_FIC digunakan saat Anda mengkonfigurasi Blok MSS DDR dalam mode Single Date Rate (SDR). Dalam konfigurasi ini, MSS mengakses DRAM Kecepatan Data Tunggal eksternal atau memori Asinkron melalui pengontrol memori lunak yang dipakai dalam struktur FPGA, seperti CoreSDR_AXI. SMC_FIC adalah antarmuka AMBA budak AXI atau AHBLite. Antarmuka DDR_FIC dan SMC_FIC saling eksklusif; hanya satu yang aktif pada satu waktu.

Antarmuka FIC memungkinkan Anda memperluas Bus MSS AMBA secara alami ke dalam struktur FPGA. Ada hingga dua contoh FIC per MSS tergantung pada perangkat yang dipilih. Contoh pertama diberi nama FIC_0 (yang tersedia di setiap perangkat) dan yang kedua diberi nama FIC_1 (mungkin tidak ada di perangkat yang lebih kecil). Anda dapat mengonfigurasi FIC sebagai antarmuka AMBA APB3 atau AHBLite tergantung pada kebutuhan desain Anda. Di setiap mode, antarmuka bus master dan budak tersedia. Artinya, master di dalam fabric dapat berinteraksi dengan budak di MSS dan master di MSS dapat berinteraksi dengan budak di dalam fabric.

Setiap subsistem Antarmuka Fabric dapat beroperasi pada frekuensi jam yang berbeda, yang didefinisikan sebagai rasio jam utama MSS M3_CLK.

Arsitektur SmartFusion2 menerapkan aturan terkait domain pencatatan jam kerja antara Antarmuka Fabric dan Fabric FPGA. Dokumen ini memberikan panduan tentang cara membangun sistem tersebut dengan benar.

Level tinggi View

Gambar 1 dan Gambar 2 menunjukkan bagaimana MSS terhubung ke fabric FPGA melalui berbagai Fabric Interface Controllers (FIC). Gambar 1 menunjukkan diagram blok keseluruhan saat DDR_FIC digunakan (memori DDR eksternal) dan Gambar 2 menunjukkan diagram blok saat SMC_FIC digunakan (memori SDR eksternal).

Diagram menunjukkan sub-blok MSS yang penting untuk menghubungkan MSS ke fabric FPGA. Sub-blok FIC mungkin digunakan atau tidak dalam aplikasi Anda. Anda juga mungkin tidak menggunakan antarmuka DDR_FIC atau SMC_FIC dalam desain Anda. Namun, hal ini tidak mengubah persyaratan keseluruhan tentang cara membuat desain dengan satu atau lebih blok FIC yang digunakan dalam desain.

Gambar 1 • Diagram Blok Fabric MSS ke FPGA – Mode DDR_FIC

Gambar 1 • Diagram Blok Fabric MSS ke FPGA – Mode DDR_FIC  Gambar 2 • Diagram Blok Fabric MSS ke FPGA – Mode SMC_FIC

Gambar 2 • Diagram Blok Fabric MSS ke FPGA – Mode SMC_FIC

SPM berisi:

- Matriks AHB_Bus; semua transaksi di MSS melewati blok ini.

- Pengontrol DDR -berinteraksi dengan DDR_FIC.

- Sub-blok DDR_FIC (SMC_FIC) (digunakan jika Anda mengaktifkan fabric FPGA ke jalur DDR di konfigurator MSS_MDDR).

- Sub-blok FIC_0.

- Sub-blok FIC_1 (hanya di perangkat yang lebih besar).

- Sub-blok FIC_2 (untuk inisialisasi APB SERDES dan DDR eksternal).

- Sub-blok MSS_CCC diperlukan untuk mengkonfigurasi jam FIC relatif terhadap jam utama MSS (M3_CLK).

- Sub-blok MSS_RESET yang menghasilkan pengaturan ulang internal MSS serta sinyal MSS_RESET_N_M2F yang menggerakkan fabric FPGA.

Kain FPGA mengandung:

- Tiga sub-sistem FIC (DDR_FIC, FIC_0 dan FIC_1).

- Fabric CCC – FAB_CCC – diperlukan untuk menghasilkan jam yang menggerakkan subsistem FIC fabric FPGA serta port MCCC_CLK_BASE pada blok MSS.

- Sinyal jam referensi FAB_CCC – dapat berupa salah satu osilator dalam chip, osilator kristal eksternal, jam yang dihasilkan secara internal pada fabric atau dari luar chip.

Diagram blok juga menunjukkan jaringan jam berwarna merah dan jaringan reset berwarna biru tua.

Dokumen ini membahas masing-masing blok ini dan menjelaskan cara menghubungkan jam dan mengatur ulang.

Pengonfigurasi MSS

Dokumen ini mengacu pada sub-blok MSS tertentu yang harus dikonfigurasi sebagai bagian dari pembuatan desain di mana MSS berinteraksi dengan fabric FPGA melalui sub-blok FIC. Blok-blok tersebut disorot dengan warna merah pada Gambar 1-1.

Gambar 1-1 • Konfigurator MSS

Gambar 1-1 • Konfigurator MSS

Tindakan SmartDesign dan MSS Configurator

Ada beberapa tindakan umum yang dirujuk dalam dokumen ini; mereka dirangkum dalam daftar berikut :. Jika Anda sudah familiar dengan SmartDesign dan MSS, Anda dapat melompat ke bagian berikutnya.

Membuat instance inti – Tindakan memilih inti dari katalog IP SoC Libero, menyeret dan melepaskan inti tersebut ke Kanvas SmartDesign.

Mengonfigurasi inti – Tindakan membuka konfigurator untuk instance inti tersebut di Canvas, memilih konfigurasi tertentu dan menjalankannya dengan mengklik OK di kotak dialog konfigurator. Sebagai hasil dari tindakan tersebut, hanya port yang berkaitan dengan konfigurasi saat ini yang terlihat dan tersedia untuk digunakan.

Membuat instance komponen – Tindakan memilih komponen dalam Hierarki Desain SoC Libero, menyeret dan melepaskan komponen tersebut ke kanvas SmartDesign.

Membuat instance komponen khusus yang sesuai dengan AMBA – Tindakan memilih komponen HDL+ di Hierarki Desain SoC Libero, menyeret dan melepaskan komponen tersebut ke Kanvas SmartDesign.

Menggunakan fitur HDL+ memungkinkan Anda menambahkan Antarmuka Bus (BIF) yang sesuai dengan AMBA ke modul HDL reguler Anda.

Mengonfigurasi komponen – Tindakan membuka konfigurator untuk komponen yang dibuat pada SmartDesign Canvas atau dari Design Hierarchy, memilih konfigurasi tertentu dan menjalankannya dengan mengklik OK di kotak dialog konfigurator. Sebagai akibat dari tindakan tersebut, semua instance pada komponen tersebut dalam proyek SoC Libero terpengaruh dan perlu diperbarui. Ketika sebuah instance diperbarui dengan komponen terbaru, hanya port yang berkaitan dengan konfigurasi saat ini yang terlihat dan tersedia untuk digunakan.

Mengaktifkan sub-blok MSS – Beberapa sub-blok MSS dapat diaktifkan atau dinonaktifkan, menunjukkan bahwa sub-blok tersebut digunakan dalam aplikasi saat ini. Semua sub-blok yang tidak digunakan harus dinonaktifkan.

Mengonfigurasi sub-blok MSS – Tindakan membuka konfigurator untuk sub-blok tersebut di konfigurator MSS, memilih konfigurasi tertentu dan melakukannya dengan mengklik OK di kotak dialog konfigurator, lalu menyimpan konfigurasi MSS. Sebagai hasil dari tindakan ini, komponen MSS memiliki konfigurasi baru dan kemungkinan antarmuka port baru. Ketika instance MSS diperbarui dengan komponen terbaru, hanya port MSS yang berkaitan dengan konfigurasi saat ini yang terlihat dan tersedia untuk digunakan.

Membuat sub-sistem fabric FPGA – Tindakan membuat instance, mengonfigurasi inti dan komponen dalam SmartDesign Canvas dan menghubungkannya bersama-sama dan ke komponen MSS yang sudah dibuat dalam SmartDesign tersebut.

Mengonfigurasi Sub-Sistem DDR_FIC

Untuk mengonfigurasi/membuat subsistem DDR_FIC, Anda harus:

- Konfigurasikan MSS MDDR untuk mengekspos antarmuka DDR_FIC

- Buat sub-sistem DDR_FIC fabric FPGA termasuk instantiasi/konfigurasi/konektivitas untuk:

– Bus AXI atau AHBLite

– Master bus AXI atau AHBLite

– Master dan periferal lain di bus sesuai kebutuhan aplikasi Anda

– Jam dan reset; lihat “Mengonfigurasi Jam Sub-Sistem FIC” pada halaman 23 dan “Mengonfigurasi Reset Sub-Sistem FIC” pada halaman 27

Langkah-langkah ini dijelaskan secara rinci di bawah ini.

Langkah 1: Konfigurasikan Sub-blok MSS MDDR untuk Mengekspos Antarmuka Bus DDR_FIC

Antarmuka DDR_FIC diekspos saat aplikasi Anda perlu mengakses memori DDR eksternal dari fabric FPGA. Dalam konfigurasi ini, sub-blok MDDR memperlihatkan antarmuka DDR_FIC, yang merupakan slave AXI atau AHBLite Bus Interface (BIF) (Gambar 3-1).

Gambar 3-1 • Konfigurasi MSS DDR dengan Akses dari FPGA Fabric

Gambar 3-1 • Konfigurasi MSS DDR dengan Akses dari FPGA Fabric

Langkah 2: Buat Sub-Sistem FPGA Fabric DDR_FIC

Berdasarkan jenis koneksi bus FPGA yang Anda pilih – AXI, Single AHBLite atau Two AHBLite – Anda harus membuat subsistem yang sesuai dengan pilihan Anda.

Sub-Sistem DDR_FIC/AXI

- Buat instance dan konfigurasikan inti IP CoreAXI dari jendela Katalog. Aktifkan slot yang ingin Anda gunakan untuk aplikasi Anda serta jumlah memori per slot yang sesuai dengan kebutuhan desain Anda. Karena Anda menangani memori DDR eksternal, pemilihan ukuran slot Anda harus sesuai dengan ruang yang Anda rencanakan untuk ditangani dari master fabric FPGA. (Gambar 3-2).

Gambar 3-2 • Konfigurasi CoreAXI

Gambar 3-2 • Konfigurasi CoreAXI - Buat instance dan konfigurasikan inti master atau komponen yang sesuai dengan AMBA AXI yang dimaksudkan untuk dikuasai ke bus AXI. Jika aplikasi Anda memerlukan lebih dari satu master ke bus CoreAXI, buat instance master kedua juga.

- Hubungkan sub-sistem:

– Hubungkan port M0 (M1) mirrored-master Bus Interface (BIF) CoreAXI ke port BIF master instans inti master Anda (Gambar 3-3).

– Hubungkan port BIF slave MSS DDR_FIC – MDDR_DDR_AXI_SLAVE – ke slot mirrored-slave bus CoreAXI yang sesuai sesuai kebutuhan peta memori Anda. Jika Anda memiliki budak lain di bus itu, sambungkan juga, sesuai peta memori Anda.

– Jam dan reset; lihat “Mengonfigurasi Jam Sub-Sistem FIC” pada halaman 23 dan “Mengonfigurasi Reset Sub-Sistem FIC” pada halaman 27.

Gambar 3-3 • Sub-Sistem DDR_FIC AXI

Gambar 3-3 • Sub-Sistem DDR_FIC AXI

Sub-sistem DDR_FIC/Single-AHBLite

- Buat instance dan konfigurasikan inti IP CoreAHBLite dari Katalog. Aktifkan slot yang ingin Anda gunakan untuk aplikasi Anda seperti yang ditunjukkan pada Gambar 3-4. Dalam mantan iniample, CoreAHBLite dikonfigurasi untuk menangani satu ruang memori DDR RAM 4GB menggunakan slot0 dari master M0. Karena Anda menangani memori DDR eksternal, pemilihan ukuran slot Anda harus sesuai dengan jumlah ruang memori DDR yang Anda rencanakan untuk ditangani dari master fabric FPGA.

Gambar 3-4 • Core AHBLite – Konfigurasi Master Wilayah Gabungan

Gambar 3-4 • Core AHBLite – Konfigurasi Master Wilayah Gabungan - Buat instance dan konfigurasikan inti master atau komponen yang sesuai dengan AMBA AHBLite yang dimaksudkan untuk dikuasai ke bus CoreAHBLite. Jika aplikasi Anda memerlukan lebih dari satu master ke bus CoreAHBLite, buat instance master tambahan juga. Hingga empat master didukung pada bus CoreAHBLite.

- Hubungkan sub-sistem:

– Hubungkan port M0 (M1) mirrored-master Bus Interface (BIF) CoreAHBLite ke port BIF master instans inti master Anda.

– Hubungkan port BIF slave MSS DDR_FIC – MDDR_DDR_AHB0_SLAVE – ke slot mirrored-slave bus CoreAHBLite yang tepat (S0 pada contoh iniample) sesuai kebutuhan peta memori Anda. Jika Anda memiliki budak lain di bus itu, sambungkan mereka sesuai peta memori Anda.

– Jam dan reset; lihat “Mengonfigurasi Jam Sub-Sistem FIC” pada halaman 23 dan “Mengonfigurasi Reset Sub-Sistem FIC” pada halaman 27.

Gambar 3-5 • Sub-Sistem DDR_FIC AHBLite

Gambar 3-5 • Sub-Sistem DDR_FIC AHBLite

DDR_FIC/Dua Sub-Sistem AHBLite

Saat Anda memilih dua opsi Antarmuka AHBLite untuk MDDR, BIF tambahan, MDDR_DDR_AHB1_SLAVE BIF, diekspos pada komponen MSS agar Anda dapat menyambung ke budak baru.

Untuk konfigurasi ini, ulangi langkah-langkah untuk konfigurasi AHBLite tunggal untuk Antarmuka BIF MDDR_DDR_AHB1_SLAVE yang diekspos pada komponen MSS.

Meskipun SMC_FIC dapat digunakan sebagai antarmuka bus AXI atau AHBLite, dokumen ini hanya menjelaskan cara menggunakan antarmuka SMC_FIC yang dikonfigurasi dalam mode AXI untuk terhubung ke inti CoreSDR_AXI. Inti tersebut adalah pengontrol RAM SDR berbasis AXI yang digunakan untuk menghubungkan, dalam hal ini, MSS ke komponen memori Single Data Rate (SDR) eksternal. Anda dapat dengan mudah menyimpulkan cara menggunakan antarmuka AHBLite dari uraian berikut; langkah-langkahnya sangat mirip. Antarmuka AXI adalah antarmuka yang lebih efisien dan merupakan opsi yang disukai.

Untuk mengonfigurasi/membuat subsistem SMC_FIC, Anda harus:

- Konfigurasikan MSS MDDR untuk mengekspos antarmuka SMC_FIC

- Buat sub-sistem DDR_FIC fabric FPGA, termasuk instantiasi/konfigurasi/konektivitas untuk:

– Bus CoreAXI

– IntiSDR_AXI

– Master dan periferal lain di bus sesuai kebutuhan aplikasi Anda

– Jam dan reset; lihat “Mengonfigurasi Jam Sub-Sistem FIC” pada halaman 23 dan “Mengonfigurasi Reset Sub-Sistem FIC” pada halaman 27

Langkah-langkah ini dijelaskan secara rinci di bawah ini.

Langkah 1: Konfigurasikan Sub-blok MSS MDDR untuk Mengekspos Antarmuka Bus SMC_FIC

Antarmuka SMC_FIC diekspos saat aplikasi Anda perlu mengakses memori SDR eksternal melalui fabric FPGA. Dalam konfigurasi ini, sub-blok MDDR memperlihatkan antarmuka SMC_FIC, yang merupakan master AXI atau AHBL Bus Interface (BIF) (Gambar 4-1).

- Klik kanan Pengontrol MDDR di dalam MSS Configurator dan pilih Konfigurasi.

- Pilih Gunakan Antarmuka AXI.

- Klik OK.

Gambar 4-1 • Konfigurasi Pengontrol Memori Lunak MDDR

Gambar 4-1 • Konfigurasi Pengontrol Memori Lunak MDDR

- Perbarui komponen MSS dengan perubahan.

(Klik kanan Komponen MSS dan pilih Perbarui Instans dengan Komponen Terbaru). MDDR_SMC_AXI_MASTER diekspos sebagai Port Antarmuka Bus dari komponen MSS.

Langkah 2: Buat Sub-Sistem FPGA Fabric SMC_FIC

- Buat instance dan konfigurasikan CoreAXI sedemikian rupa sehingga slot master M0 diaktifkan untuk slot slave S0, seperti yang ditunjukkan pada Gambar 4-2. Karena Anda menangani memori eksternal melalui pengontrol memori lunak, pemilihan ukuran slot Anda harus sesuai dengan jumlah ruang memori eksternal yang Anda rencanakan untuk ditangani dari prosesor Cortex-M3 atau penulisan master apa pun ke memori eksternal tersebut melalui jembatan MSS DDR.

Gambar 4-2 • Konfigurasi CoreAXI – Mode SMC_FIC

Gambar 4-2 • Konfigurasi CoreAXI – Mode SMC_FIC - Dari Katalog IP, buat instance dan konfigurasikan CoreSDR_AXI agar sesuai dengan parameter memori eksternal Anda.

- Hubungkan sub-sistem (Gambar 4-3):

– Hubungkan port BIF master MSS SMC_FIC – MDDR_SMC_AXI_MASTER – ke bus CoreAXI mirrored-master M0.

– Hubungkan port S0 mirrored-slave Bus Interface (BIF) CoreAXI ke port BIF slave dari instans inti CoreSDR_AXI.

– Jam dan reset; lihat “Mengonfigurasi Jam Sub-Sistem FIC” pada halaman 23 dan “Mengonfigurasi Reset Sub-Sistem FIC” pada halaman 27.

Gambar 4-3 • Koneksi Sub-Sistem SMC_FIC

Gambar 4-3 • Koneksi Sub-Sistem SMC_FIC

Mengonfigurasi Sub-Sistem FIC

Untuk mengonfigurasi/membuat subsistem FIC, Anda harus:

- Konfigurasikan MSS FIC untuk mengekspos antarmuka FIC

- Buat sub-sistem FIC fabric FPGA termasuk instantiasi/konfigurasi/konektivitas untuk:

– Bus APB3 atau AHBLite

– Konfigurasi master dan/atau periferal yang sesuai dengan APB3 dan AHBLite serta koneksi ke bus sesuai kebutuhan aplikasi Anda

– Jam dan reset; lihat “Mengonfigurasi Jam Sub-Sistem FIC” pada halaman 23 dan “Mengonfigurasi Reset Sub-Sistem FIC” pada halaman 27

Langkah-langkah ini dijelaskan secara rinci di bawah ini.

Langkah 1: Konfigurasikan Sub-Blok MSS FIC

- Panggil FIC Configurator dan klik kanan pada FIC_0 atau FIC_1 untuk membuka FIC Configurator.

- Di grup konfigurasi Configurator untuk MSS ke FPGA Fabric Interface, pilih:

– Tipe antarmuka AHBLite atau APB3

– Apakah Anda bermaksud menggunakan antarmuka sebagai master dari struktur FPGA

– Apakah Anda bermaksud menggunakan antarmuka sebagai slave yang dikuasai oleh fabric FPGA (Gambar 5-1)

Gambar 5-1 • Opsi Antarmuka Fabric MSS ke FPGA

Gambar 5-1 • Opsi Antarmuka Fabric MSS ke FPGA - Jika Anda menggunakan Antarmuka AHBLite, Anda juga dapat menggunakan Opsi AHBLite Tingkat Lanjut untuk memilih mode bypass, atau mengekspos port ID master jika Anda memilih antarmuka untuk bertindak sebagai master fabric (Gambar 5-2).

Gambar 5-2 • Opsi AHBLite Tingkat Lanjut

Gambar 5-2 • Opsi AHBLite Tingkat Lanjut

Langkah 2: Buat Sub-Sistem FIC Fabric FPGA

Untuk setiap antarmuka FIC yang diekspos – master dan slave, Anda harus membuat instance bus (CoreAHBLite atau CoreAPB3) yang cocok dengan tipe yang Anda pilih. Tergantung pada peran antarmuka (master/slave) dan tipe (AHBLite/APB3), bus harus dikonfigurasi sebagai berikut:

Guru/AHBLite

Buat instance dan konfigurasikan bus CoreAHBLite sebagai berikut:

- Pilih opsi Ruang Memori yang sesuai dengan kebutuhan Anda:

– Jika Anda memerlukan ruang alamat kurang dari 16 MB untuk semua periferal Anda, pilih opsi seperti yang ditunjukkan pada Gambar 5-3. Mode ini menyediakan 16 slot 16MB yang dapat digunakan untuk menghubungkan hingga 16 AHBLite slave.

Gambar 5-3 • Konfigurasi Ruang Memori Master/AHBLite – 16 MB per slot

Gambar 5-3 • Konfigurasi Ruang Memori Master/AHBLite – 16 MB per slot

– Jika Anda memerlukan ruang alamat lebih dari 16 MB dan kurang dari 256 MB untuk periferal mana pun, pilih opsi seperti yang ditunjukkan pada Gambar 5-4. Mode ini menyediakan 16 slot 256 MB yang dapat digunakan untuk menghubungkan hingga 16 budak AHBLite.

Gambar 5-4 • Konfigurasi Ruang Memori Master/AHBLite – 256 MB per slot

Gambar 5-4 • Konfigurasi Ruang Memori Master/AHBLite – 256 MB per slot - Aktifkan slot yang Anda gunakan untuk aplikasi Anda (Gambar 5-5). Praktik terbaiknya adalah menggunakan M1 untuk memasukkan akses seperti yang ditunjukkan pada Gambar 4-2 di halaman 15.

Catatan: Gunakan M1 jika Anda berencana membuat subsistem multi master di mana Anda memiliki master di fabric yang memerlukan fitur remap sehingga perlu dihubungkan ke M0.

– Jika Anda telah memilih opsi 16 MB per slot, tidak ada batasan slot mana yang dapat digunakan.

– Jika Anda telah memilih opsi 256 MB per slot, hanya slot yang kompatibel dengan pilihan wilayah alamat memori fabric instans FIC yang dapat digunakan. Setiap wilayah alamat memori FIC berukuran 256 MB. Keenam wilayah memori FIC dirangkum dalam Tabel 5 -1.

Tabel 5-1 • Wilayah Alamat dan Slot yang Kompatibel untuk 256 MB per Opsi Slot

Wilayah Alamat Memori Slot yang Kompatibel 30000000-3FFFFFFFF 3 50000000-5FFFFFFFF 5 70000000-7FFFFFFFF 7 80000000-8FFFFFFFF 8 90000000-9FFFFFFFF 9 F0000000-FFFFFFFF 15 (P)  Gambar 5-5 • Konfigurasi Akses Master/AHBLite Master

Gambar 5-5 • Konfigurasi Akses Master/AHBLite Master - Buat instance dan konfigurasikan inti periferal yang sesuai dengan AHBLite dan/atau komponen khusus yang sesuai dengan AHBLite.

- Hubungkan sub-sistem:

– Hubungkan port M1 mirrored-master Bus Interface (BIF) CoreAHBLite ke port BIF master MSS – FIC_0/1_AHB_MASTER – seperti yang ditunjukkan pada Gambar 5-6.

– Hubungkan budak AHBLite ke slot yang tepat sesuai kebutuhan peta memori Anda.

– Jam dan reset; lihat “Mengonfigurasi Jam Sub-Sistem FIC” pada halaman 23 dan “Mengonfigurasi Reset Sub-Sistem FIC” pada halaman 27.

Gambar 5-6 • Sub-Sistem FIC Master/AHBLite

Gambar 5-6 • Sub-Sistem FIC Master/AHBLite

Induk/APB3

Buat instance dan konfigurasikan bus CoreAPB3 sebagai berikut:

- Pilih opsi Konfigurasi Alamat seperti yang ditunjukkan pada Gambar 5-7. Mode ini menyediakan enam belas slot 16MB yang dapat digunakan untuk menghubungkan hingga enam belas budak yang sesuai dengan APB3. Jika Anda memerlukan slot dengan lebih banyak memori, Anda dapat menggabungkan beberapa budak untuk membuat slot yang lebih besar. Lihat Panduan Pengguna CoreAPB3 untuk rincian lebih lanjut tentang opsi ini.

Gambar 5-7 • Konfigurasi Alamat Master/APB3

Gambar 5-7 • Konfigurasi Alamat Master/APB3 - Aktifkan slot yang Anda gunakan untuk aplikasi Anda, seperti yang ditunjukkan pada Gambar 5-8.

Gambar 5-8 • Konfigurasi Slot Master/APB3 Slave

Gambar 5-8 • Konfigurasi Slot Master/APB3 Slave - Membuat instance dan mengonfigurasi inti periferal yang sesuai dengan APB3 dan/atau komponen khusus yang sesuai dengan APB3.

- Hubungkan sub-sistem:

– Hubungkan port Mirrored-master Bus Interface (BIF) CoreAPB3 ke port BIF master MSS FIC_0/1_APB_MASTER – seperti yang ditunjukkan pada Gambar 5-9.

– Hubungkan budak APB3 ke slot yang tepat sesuai kebutuhan peta memori Anda.

– Jam dan reset; lihat “Mengonfigurasi Jam Sub-Sistem FIC” pada halaman 23 dan “Mengonfigurasi Reset Sub-Sistem FIC” pada halaman 27.

Gambar 5-9 • Subsistem FIC Master/APB3

Gambar 5-9 • Subsistem FIC Master/APB3

Budak/AHBLite

Tidak tersedia saat ini.

Budak/APB3

Tidak tersedia saat ini.

Mengonfigurasi Jam Sub-Sistem FIC

Untuk membuat konfigurasi jam dan konektivitas yang tepat, Anda harus:

- Konfigurasikan jam MSS CCC FIC

- Membuat instance dan mengonfigurasi inti CCC fabric FPGA

- Hubungkan jaringan jam untuk setiap sub-sistem FIC

- Hubungkan port MSS CLK_BASE ke jaringan jam sub-sistem FIC fabric FPGA yang benar

Arsitektur SmartFusion2 menerapkan sejumlah aturan yang harus diikuti agar semua subsistem FIC dapat berinteraksi dengan baik antara logika MSS dan logika fabric FPGA. Aturan-aturan ini didefinisikan di bawah ini dan ditunjukkan pada Gambar 6-1.

- Setiap sub-sistem FIC fabric FPGA harus digerakkan oleh jam yang frekuensi jamnya sesuai dengan frekuensi yang ditentukan, untuk sub-sistem tertentu, dalam konfigurator MSS CCC.

- Semua jam sub-sistem FIC fabric FPGA harus disejajarkan dengan tepat; frekuensi jam mungkin berbeda, namun tepi naik pada jam yang lebih lambat harus sejajar dengan tepi naik pada jam tercepat.

- Jam sub-sistem FIC fabric FPGA dengan frekuensi terkecil harus menggerakkan MSS CLK_BASE.

- Jika jam fabric berasal dari CCC fabric (dengan PLL), output fabric CCC LOCK harus dihubungkan ke port MSS_CCC_CLK_BASE_PLL_LOCK. Sirkuit Jam Penyelarasan Kain MSS CCC (FACC) memantau sinyal CLK_BASE PLL LOCK untuk menjamin bahwa CLK_BASE stabil sebelum beralih dari jam siaga (jam yang digunakan selama booting perangkat) ke jam yang dikonfigurasi pengguna yang berasal dari CLK_BASE.

Gambar 6-1 • Aturan Jam Sub-Sistem

Gambar 6-1 • Aturan Jam Sub-Sistem

Ikuti langkah-langkah di bawah ini untuk mengonfigurasi jaringan jam untuk semua subsistem FIC Anda.

Langkah 1: Konfigurasikan Sub-Blok MSS CCC

Untuk setiap blok FIC (FIC_0, FIC_1, dan DDR_FIC/SMC_FIC) yang digunakan dalam desain Anda, pilih pembagi jam di MSS Clock Configurator (MSS_CCC) seperti yang ditunjukkan pada Gambar 6-2. Gambar 6-2 • Konfigurasi Jam MSS CCC FIC

Gambar 6-2 • Konfigurasi Jam MSS CCC FIC

Catatan bahwa bidang CLK_BASE tidak dapat diedit. Frekuensi CLK_BASE, sebagaimana ditentukan oleh arsitektur SmartFusion2, harus merupakan frekuensi minimum dari semua frekuensi jam FIC dan secara otomatis dihitung oleh konfigurator MSS CCC. Lihat “Langkah 3: Hubungkan Jaringan Jam Subsistem FIC Fabric FPGA” di halaman 25 untuk detail lebih lanjut tentang konfigurasi CLK_BASE.

Langkah 2: Konfigurasikan jam FIC Fabric FPGA

Buat instance CCC fabric (dengan PLL) dan konfigurasikan untuk memenuhi aturan jam sub-sistem FIC yang dijelaskan di halaman 23. Anda biasanya perlu mengaitkan keluaran global (GLx) untuk setiap jam FIC, tentukan frekuensinya untuk setiap keluaran ( mencocokkan frekuensi yang ditentukan dalam MSS CCC) dan memiliki semua keluaran global yang berasal dari keluaran PLL untuk menjamin penyelarasan fasa (seperti yang ditunjukkan pada Gambar 6-3).

Catatan: Jika dua sub-sistem FIC memiliki frekuensi yang sama, Anda tidak perlu menghasilkan dua output global independen dari CCC fabric; satu sudah cukup. Gambar 6-3 • CCC Kain dengan PLL

Gambar 6-3 • CCC Kain dengan PLL

Langkah 3: Hubungkan Jam Sub-Sistem FIC Fabric FPGA Jaringan

Hubungkan setiap GLx keluaran global CCC fabric ke sub-sistem FIC yang terkait dengannya.

Langkah 4: Hubungkan Port MSS CLK_BASE

Hubungkan GLx keluaran global CCC fabric yang paling lambat ke port MSS CLK_BASE.

Langkah 5: Hubungkan Port MSS MCCC_CLK_BASE_PLL_LOCK

Hubungkan keluaran CCC LOCK fabric ke port MSS MCCC_CLK_BASE_PLL_LOCK.

Persyaratan Analisis Waktu

Lakukan analisis pewaktuan statis pasca-tata letak untuk memastikan bahwa desain memenuhi persyaratan pewaktuan yang ditentukan dalam Konfigurator CCC MSS CCC dan FPGA fabric. Anda mungkin harus mengubah M3_CLK atau meningkatkan rasio jam antara MSS dan fabric untuk mendapatkan desain yang lolos Analisis Waktu Statis.

Mengonfigurasi Reset Sub-Sistem FIC

Untuk mengonfigurasi Reset Sub-Sistem FIC:

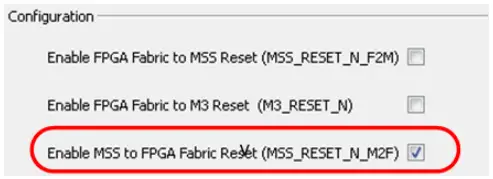

- Dari MSS Configurator, konfigurasikan sub-blok MSS Reset untuk mengekspos port MSS_RESET_N_M2F.

Gambar 7-1 • Konfigurasikan Sub-Blok MSS Reset

Gambar 7-1 • Konfigurasikan Sub-Blok MSS Reset - Hubungkan port MSS_RESET_N_M2F ke semua port reset sub-sistem FIC fabric FPGA.

Mengonfigurasi Peta Memori Sistem

Setiap periferal (budak AMBA AXI, AHBLite dan APB3) diidentifikasi dengan alamat dari titik master subsistem FIC view. Kita biasanya mengacu pada hubungan keseluruhan antara tuan dan budak dari suatu subsistem sebagai peta memori subsistem tersebut. Peta memori subsistem dapat diedit di SmartDesign. Anda juga bisa view peta memori akhir sistem Anda saat Anda membuat seluruh sistem. Peta memori adalah bagian dari Lembar Data yang dihasilkan untuk 'akar' desain Anda dari generasi ke generasi.

Mengonfigurasi Peta Memori (Perilaku SmartDesign Generik)

Dalam SmartDesign, periferal diberi alamat pada bus berdasarkan alamat dasar bus tersebut dalam sub-sistem ditambah nomor slot pada bus tersebut dikalikan dengan ukuran slot. Jadi mengubah nomor slot untuk suatu periferal akan mempengaruhi alamatnya. Mengubah penetapan slot untuk periferal dapat dilakukan dengan menyambungkan secara manual BIF budak periferal ke BIF (slot) budak cermin bus tertentu menggunakan alat konektivitas SmartDesign yang tersedia di Canvas. Hal ini juga dapat dilakukan dengan mengedit peta memori menggunakan Modify Memory Map, seperti yang ditunjukkan pada Gambar 8-1. Gambar 8-1 • Memodifikasi Memory Map dari SmartDesign Canvas

Gambar 8-1 • Memodifikasi Memory Map dari SmartDesign Canvas

Kotak dialog Modify Memory Map muncul (Gambar 8-2). Gambar 8-2 • Kotak Dialog Modifikasi Peta Memori

Gambar 8-2 • Kotak Dialog Modifikasi Peta Memori

Mengonfigurasi Wilayah Memori untuk Antarmuka FIC (MSS Master View)

Ada enam wilayah 256 MB yang ditetapkan sebagai Wilayah FIC 0 hingga 5 di peta memori MSS. Masing-masing wilayah ini dapat dialokasikan ke antarmuka budak FIC_0 atau FIC_1 dengan cara yang saling eksklusif. Anda dapat memilih antarmuka budak FIC (0 atau 1) mana yang Anda tetapkan wilayah tersebut dengan menggunakan tombol radio di sebelah setiap wilayah di Wilayah Alamat Fabric FPGA (MSS Master View) kotak grup (Gambar 8-3).  Gambar 8-3 • Wilayah Alamat Fabric FPGA (MSS Master View)

Gambar 8-3 • Wilayah Alamat Fabric FPGA (MSS Master View)

Rumus Umum Perhitungan Peta Memori

Alamat dasar yang mungkin untuk antarmuka fabric FIC adalah 0x30000000, 0x50000000, 0x70000000, 0x80000000, 0x90000000, dan 0xF0000000. Lihat “Mengonfigurasi Sub-Sistem FIC” di halaman 17 untuk detail tentang cara mengonfigurasi setiap instans FIC untuk dipetakan ke alamat ini.

Untuk AHBLite, ukuran slotnya bisa 16 MB (0x01000000) atau 256 MB (0x10000000).

Bila menggunakan 16 MB per slot, semua slot dari 0 hingga 16 dapat digunakan; alamat perangkat klien dapat dihitung sebagai alamat dasar wilayah memori FIC + (nomor slot * 0x01000000). Dalam konfigurasi ini, semua wilayah sebenarnya merupakan alias satu sama lain karena inti AHBLite tidak mendekode bit alamat [31:28]; slot didekodekan menggunakan bit alamat [27:24].

Bila menggunakan 256 MB per slot, hanya slot 3, 5, 7, 8, 9 dan F yang dapat digunakan; alamat perangkat klien dapat dihitung sebagai alamat dasar wilayah memori FIC + (nomor slot * 0x10000000). Dalam konfigurasi ini, semua wilayah secara unik mengalamatkan slot yang berbeda karena inti AHBLite mendekode slot tersebut menggunakan bit alamat [31:28]. Dalam konfigurasi ini, untuk menyederhanakan persamaan peta memori, alamat dasarnya adalah 0x00000000, bukan salah satu dari enam alamat tetap yang ditentukan di atas.

Example 1 (konfigurasi slot 16 MB):

Menggunakan wilayah memori 0x50000000, jika periferal berada pada slot nomor 7, maka alamatnya adalah: 0x50000000 + (0x7 * 0x01000000) = 0x57000000

Example 2 (konfigurasi slot 256 MB):

Menggunakan wilayah memori 0x50000000, jika periferal berada pada slot nomor 15, maka alamatnya adalah: 0x00000000 + (0xF * 0x10000000) = 0xF0000000

Viewmelakukan Peta Memori Akhir

Saat ini, Libero SoC tidak menghasilkan peta memori yang benar untuk sistem yang menggunakan MSS SmartFusion2.

Dukungan Produk

Grup Produk SoC Microsemi mendukung produknya dengan berbagai layanan dukungan, termasuk Layanan Pelanggan, Pusat Dukungan Teknis Pelanggan, a websitus, surat elektronik, dan kantor penjualan di seluruh dunia. Apendiks ini berisi informasi tentang cara menghubungi Grup Produk SoC Microsemi dan menggunakan layanan dukungan ini.

Pelayanan pelanggan

Hubungi Layanan Pelanggan untuk dukungan produk non-teknis, seperti harga produk, peningkatan produk, informasi pembaruan, status pesanan, dan otorisasi.

Dari Amerika Utara, hubungi 800.262.1060

Dari seluruh dunia, hubungi 650.318.4460

Faks, dari mana saja di dunia, 408.643.6913

Pusat Dukungan Teknis Pelanggan

Grup Produk SoC Microsemi memiliki Pusat Dukungan Teknis Pelanggan dengan insinyur yang sangat terampil yang dapat membantu menjawab pertanyaan perangkat keras, perangkat lunak, dan desain Anda tentang Produk SoC Microsemi. Pusat Dukungan Teknis Pelanggan menghabiskan banyak waktu untuk membuat catatan aplikasi, jawaban atas pertanyaan siklus desain umum, dokumentasi masalah umum, dan berbagai FAQ. Jadi, sebelum Anda menghubungi kami, silakan kunjungi sumber daya online kami. Sangat mungkin kami telah menjawab pertanyaan Anda.

Dukungan Teknis

Kunjungi Dukungan Pelanggan weblokasi (www.microsemi.com/soc/support/search/default.aspx) untuk informasi dan dukungan lebih lanjut. Banyak jawaban tersedia di pencarian web sumber termasuk diagram, ilustrasi, dan link ke sumber lain di weblokasi.

Weblokasi

Anda dapat menelusuri berbagai informasi teknis dan non-teknis di halaman beranda SoC, di www.microsemi.com/soc.

Menghubungi Pusat Dukungan Teknis Pelanggan

Staf insinyur yang sangat terampil di Pusat Dukungan Teknis. Pusat Dukungan Teknis dapat dihubungi melalui email atau melalui Grup Produk SoC Microsemi weblokasi.

E-mail

Anda dapat mengomunikasikan pertanyaan teknis Anda ke alamat email kami dan menerima jawaban kembali melalui email, faks, atau telepon. Juga, jika Anda memiliki masalah desain, Anda dapat mengirim email desain Anda files untuk menerima bantuan. Kami terus memantau akun email sepanjang hari. Saat mengirimkan permintaan Anda kepada kami, pastikan untuk menyertakan nama lengkap, nama perusahaan, dan informasi kontak Anda untuk pemrosesan permintaan Anda secara efisien.

Alamat email dukungan teknis adalah soc_tech@microsemi.com.

Kasus Saya

Pelanggan Grup Produk SoC Microsemi dapat mengirimkan dan melacak kasus teknis secara online dengan mengunjungi Kasus Saya.

Di luar AS

Pelanggan yang membutuhkan bantuan di luar zona waktu AS dapat menghubungi dukungan teknis melalui email (soc_tech@microsemi.com) atau hubungi kantor penjualan setempat. Daftar kantor penjualan dapat ditemukan di www.microsemi.com/soc/company/contact/default.aspx.

Dukungan Teknis ITAR

Untuk dukungan teknis pada RH dan RT FPGA yang diatur oleh International Traffic in Arms Regulations (ITAR), hubungi kami melalui soc_tech_itar@microsemi.com. Atau, dalam Kasus Saya, pilih Ya di daftar drop-down ITAR. Untuk daftar lengkap Microsemi FPGA yang diatur ITAR, kunjungi ITAR web halaman.

Microsemi Corporation (NASDAQ: MSCC) menawarkan portofolio semikonduktor yang komprehensif solusi untuk: kedirgantaraan, pertahanan dan keamanan; perusahaan dan komunikasi; dan industri dan pasar energi alternatif. Produk termasuk perangkat analog dan RF berkinerja tinggi dan andal, sinyal campuran dan sirkuit terpadu RF, SoC yang dapat disesuaikan, FPGA, dan subsistem lengkap. Microsemi berkantor pusat di Aliso Viejo, California. Pelajari selengkapnya di www.microsemi.com.

© 2014 Perusahaan Mikrosemi. Seluruh hak cipta. Microsemi dan logo Microsemi adalah merek dagang dari Microsemi Corporation. Semua merek dagang dan merek layanan lainnya adalah milik dari pemiliknya masing-masing.

5-02-00370-1/08.14

Kantor Pusat Perusahaan Microsemi

Kantor Pusat Perusahaan Microsemi

Satu Perusahaan, Aliso Viejo CA 92656 USA

Di AS: +1 Telepon: 949-380-6100

Penjualan: +1 Telepon: 949-380-6136

Telp: +1 Telepon: 949-215-4996

Dokumen / Sumber Daya

|

Microsemi SmartFusion2 MSS Membuat Desain [Bahasa Indonesia:] Panduan Pengguna SmartFusion2 MSS Membuat Desain |